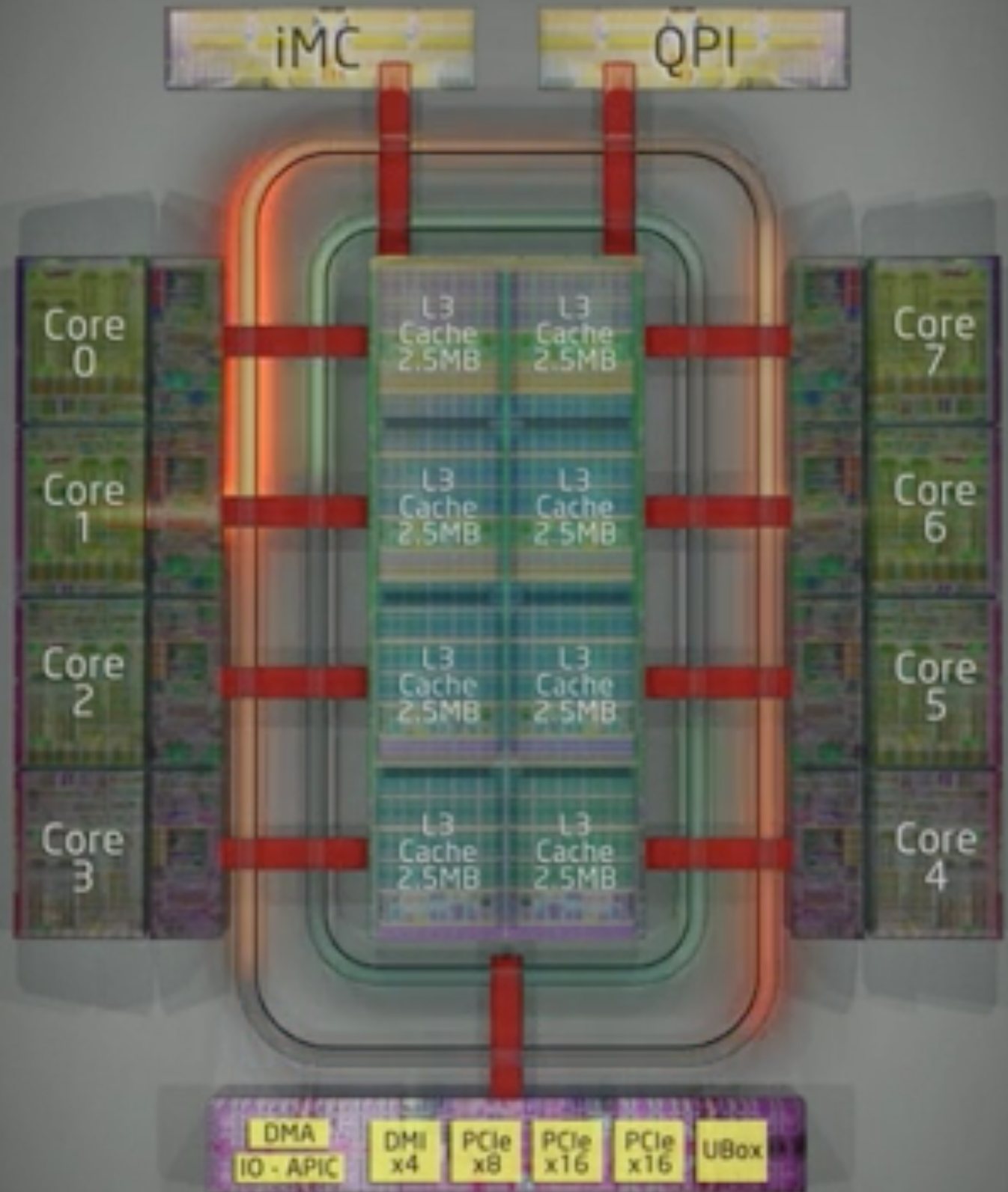

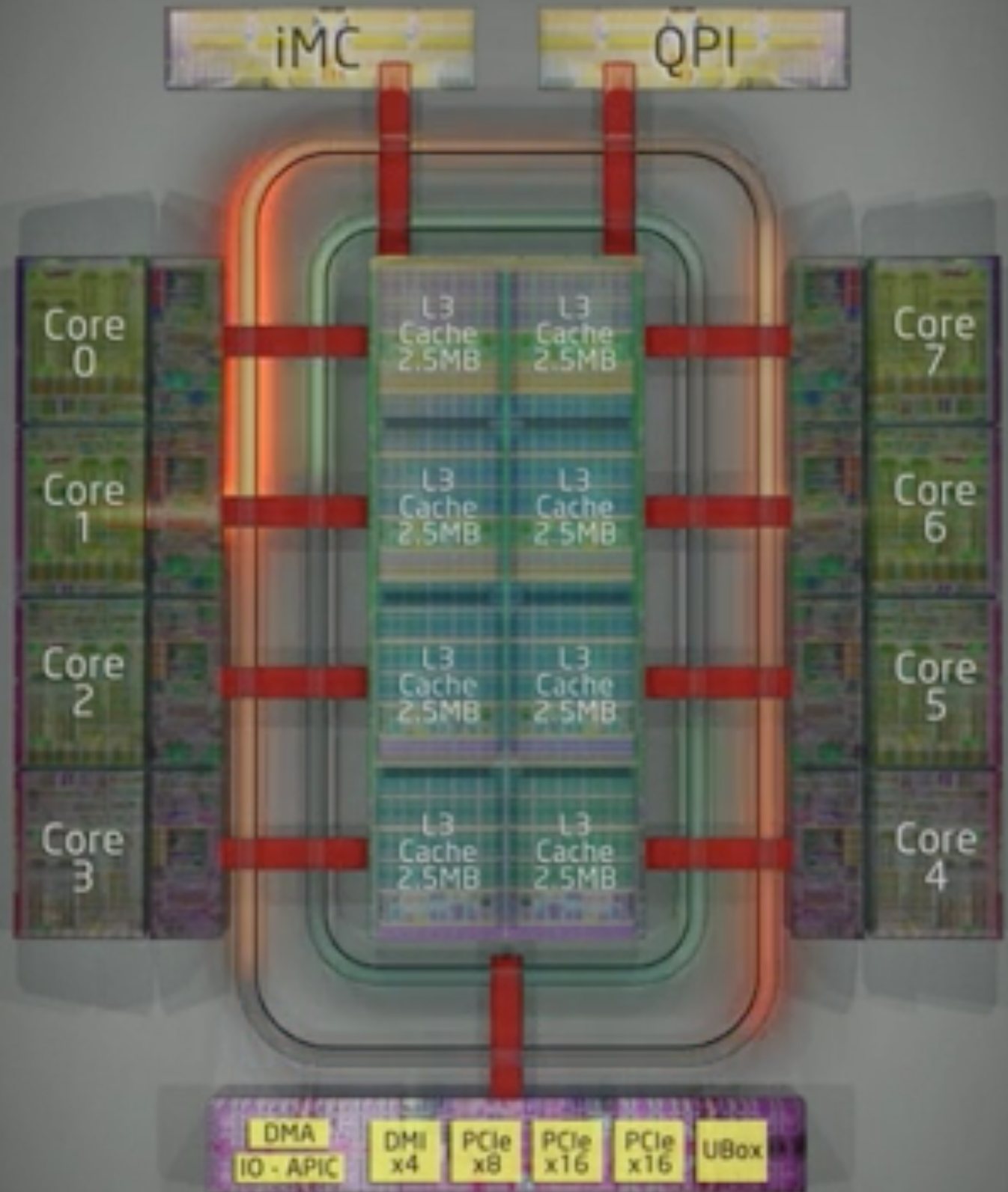

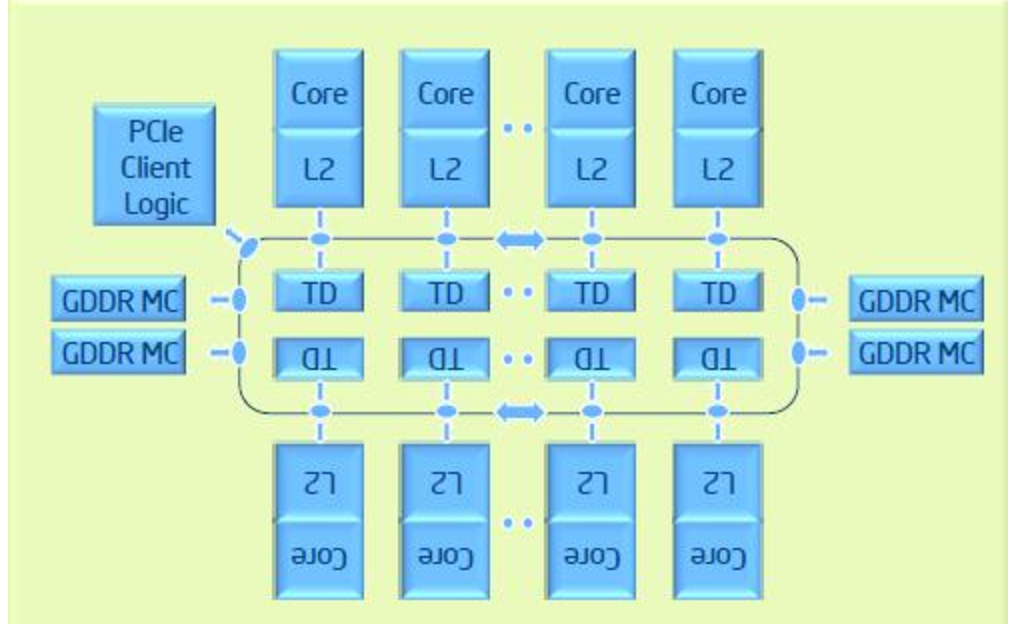

Figure 2 - ntel Xeon E5-2650v2 Architecture

| Processor |

Intel(R) Xeon(R) CPU E5-2650 v2 @ 2.60GHz |

| Operationg System |

CentOS Linux release 7.2.1511 |

| CPU cores per Processor |

8 |

| Thread(s) per core |

2 |

| Total of threads per Processor |

16 |

| Host Physical Memory |

64229 MB |

| CPU op-mode(s) |

32-bit, 64-bit |

| Host Physical Memory |

65933 MB |

| L1 dcache |

32K |

| L1 icache |

32K |

| L2 cache |

256K |

| L3 cache |

20480K |

| cache_alignment |

64 |

| address sizes |

46 bits physical, 48 bits virtual |

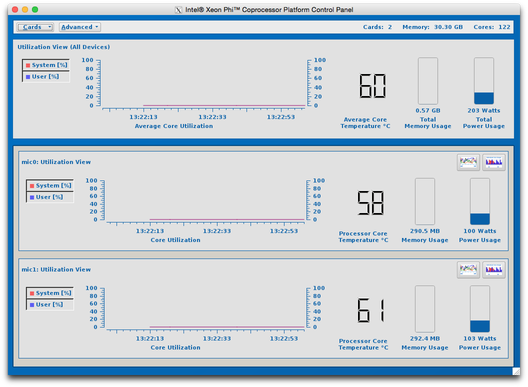

| Device Series |

Intel Xeon Phi Coprocessor 7120P 16GB 1.238GHz 61 cores 300W |

| Number of Cores |

61 |

| Threads per core (Hyper threads) |

4 |

| Total of Threads |

244 |

| Frequency |

1,24 GHz |

| Coprocessor OS Version |

2.6.38.8+mpss3.7.1 |